# Solution to Midterm 2 Exam

Dec. 2. 2014

# 1. Equivalent States [25 point]

Reduce the following state transition table to a minimum number of states. The starting state is a. The input is X. The output is Z.

| state | X = 0 | X = 1 | Z |

|-------|-------|-------|---|

| a     | с     | f     | 1 |

| b     | h     | f     | 1 |

| c     | i     | h     | 1 |

| d     | a     | e     | 0 |

| e     | e     | i     | 1 |

| f     | a     | c     | 0 |

| h     | a     | b     | 0 |

| i     | a     | b     | 0 |

| j     | c     | i     | 1 |

| b | c - h          |                |                |       |   |       |  |

|---|----------------|----------------|----------------|-------|---|-------|--|

| c | c – i<br>f – h | h – i<br>h – f |                |       |   |       |  |

| d | ×              | ×              | ×              |       |   |       |  |

| e | c – e<br>f – i | h – e<br>f – i | i – e<br>h – i | ×     |   |       |  |

| f | ×              | ×              | ×              | e - c | × |       |  |

| h | ×              | ×              | ×              | e – b | × | c - b |  |

| i | ×              | ×              | ×              | e - b | × | c - b |  |

$$a == j$$

,  $b == c$ ,  $f == h == i$

Additionally, d, e, and j will never be reached because the starting state is a.

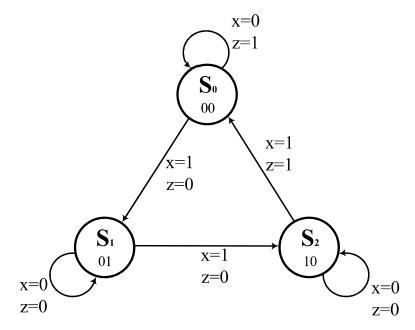

# 2. Mealy State Machine Design [25 point]

Design a finite state machine that accepts an input binary sequence such as 001010011101... Its output is zero except when the number of 1's that have been seen is a multiple of three. For example

#### Input X:

## Output Z:

- (a) Draw a state transition diagram.

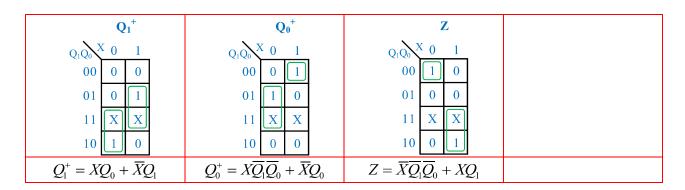

- (b) Write a truth table for computing the input to D flip-fops for the next states.

- (c) Write a truth table for computing the input to JK flip-fops for the next states.

- (d) Write a truth table for computing the output.

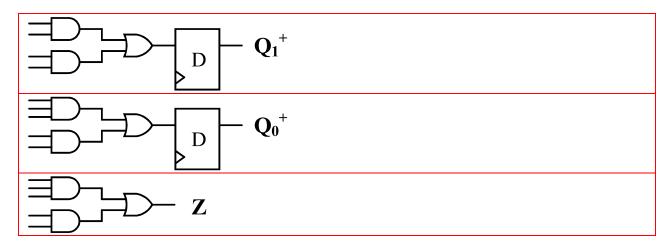

- (e) Implement the circuit with D flip-flops.

- (f) Implement the circuit with JK flip-flops.

| $\mathbf{Q}_1$ | $Q_0$ | X | $\mathbf{Q_1}^+$ | ${f Q_0}^+$ | $J_1$ | $K_1$ | $J_0$ | $-\mathbf{K}_0$ | Z |

|----------------|-------|---|------------------|-------------|-------|-------|-------|-----------------|---|

| 0              | 0     | 0 | 0                | 0           | 0     | X     | 0     | X               | 1 |

| 0              | 0     | 1 | 0                | 1           | 0     | X     | 1     | X               | 0 |

| 0              | 1     | 0 | 0                | 1           | 0     | X     | X     | 0               | 0 |

| 0              | 1     | 1 | 1                | 0           | 1     | X     | X     | 1               | 0 |

| 1              | 0     | 0 | 1                | 0           | X     | 0     | 0     | X               | 0 |

| 1              | 0     | 1 | 0                | 0           | X     | 1     | 0     | X               | 1 |

| 1              | 1     | 0 | X                | X           | X     | X     | X     | X               | X |

| 1              | 1     | 1 | X                | X           | X     | X     | X     | X               | X |

| $J_1$            | $\mathbf{K}_{1}$ | $\mathbf{J_0}$          | $\mathbf{K}_0$   |

|------------------|------------------|-------------------------|------------------|

| $Q_1Q_0$ $X = 0$ | $Q_1Q_0$ $X = 0$ | $Q_1Q_0^X = 0$          | $Q_1Q_0$ $X$ 0 1 |

| 00 0 0           | 00 X 1           | 00 0 1                  | 00 X X           |

| 01 0 1           | 01 X X           | 01 X X                  | 01 0 1           |

| 11 X X           | 11 X X           | 11 X X                  | 11 X X           |

| 10 X X           | 10 0 1           | 10 0 0                  | 10 X X           |

| $J_1 = XQ_0$     | $K_1 = X$        | $J_0 = X\overline{Q}_1$ | $K_0 = X$        |

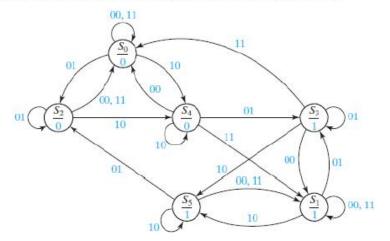

## 3. Moore State Machine Design [25 point]

Solution

The only sequences of input pairs which affect the output are of length two. Therefore, the previous and present inputs will determine the output, and the circuit must remember only the previous input pair. At first, it appears that three states are required, corresponding to the last input received being  $X_1X_2 = 01,10$  and (00 or 11). Note that it is unnecessary to use a separate state for 00 and 11 because neither input starts a sequence which leads to an output change. However, for each of these states the output could be either 0 or 1, so we will initially define six states as follows:

| Previous         | Output | State                 |

|------------------|--------|-----------------------|

| Input $(X_1X_2)$ | (Z)    | Designation           |

| 00 or 11         | 0      | S <sub>0</sub>        |

| 00 or 11         | 1      | 5,                    |

| 01               | 0      | S <sub>2</sub>        |

| 01               | 1      | <b>S</b> <sub>3</sub> |

| 10               | 0      | 54                    |

| 10               | 1      | S                     |

Using this state designation, we can then set up a state table (Table 14-7). The six-row table given here can be reduced to five rows, using the methods given in Unit 15.

TABLE 14-7

© Cengage Learning 2014

| Present        |   | Next State     |                |    |    |  |  |

|----------------|---|----------------|----------------|----|----|--|--|

| State          | Z | $X_1X_2=00$    | 01             | 11 | 10 |  |  |

| So             | 0 | So             | Sz             | So | S4 |  |  |

| S <sub>1</sub> | 1 | S <sub>1</sub> | S <sub>3</sub> | 51 | 55 |  |  |

| S2             | 0 | So             | 52             | 50 | 54 |  |  |

| 53             | 1 | 51             | 53             | 50 | 55 |  |  |

| 54             | 0 | 50             | 53             | 51 | 54 |  |  |

| 55             | 1 | 51             | 52             | 51 | 55 |  |  |

The  $S_4$  row of this table was derived as follows. If 00 is received, the input sequence has been 10,00, so the output does not change, and we go to  $S_0$  to remember that the last input received was 00. If 01 is received, the input sequence has been 10,01, so the output must change to 1, and we go to  $S_3$  to remember that the last input received was 01. If 11 is received, the input sequence has been 10,11, so the output should become 1, and we go to  $S_1$ . If 10 is received, the input sequence has been 10,10, so the output does not change, and we remain in  $S_4$ . Verify for yourself that the other rows in the table are correct. The state graph is shown in Figure 14-18.

FIGURE 14-18 State Graph for Example 3

Cengage Learning 2014

## 4. An Arithmetic Circuit [25 point]

The *Collatz* conjecture is a famous open problem in mathematics, proposed by Lothar Collatz in 1937. Consider the following iterative procedure. For any positive integer *x*,

```

if x is odd, let x = 3x + 1;

else let x = x / 2.

```

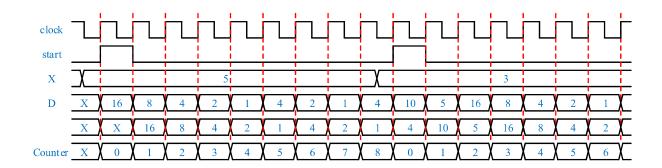

The conjecture is that, starting with any positive integer x, the procedure always terminates with x = 1. For instance, starting with x = 5, one follows the sequence 16, 8, 4, 2 and 1.

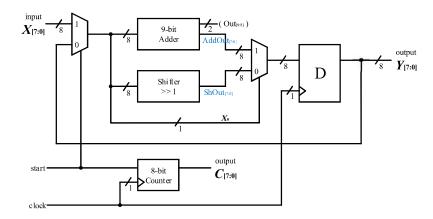

- (a) Design a combinational circuit to implement a **single step** of the *Collatz* procedure, as follows. Let the bits  $X = (X_0, \ldots, X_7)$  represent the initial value of x, least significant bit first. Let the bits  $Y = (Y_0, \ldots, Y_7)$  represent the results, either 3X + 1 or X / 2.

- (b) Design a sequential circuit that **iterates** through the *Collatz* procedure. Design your circuit with inputs X, start and clock, and output Y. When start is set to 1, your circuit should read the initial value  $X = (X_0, ..., X_7)$ . Then, when start is set to 0, your circuit should iterate through the *Collatz* procedure one iteration per clock cycle indefinitely. It should **wrap around** 256: if the expected value of X is greater than 255, the value should be set to X 256. If the value is 1, let it compute 3X + 1 = 4 and keep going.

- (c) Add a 8-bit counter with outputs  $C_0$ , ...,  $C_7$  to your design. When *start* is set to 1, the counter should get cleared. Then it should count up for every iteration. Let it wrap around 256.

| a. 'start' / Feedback connection with Mux                    | (3pt) |

|--------------------------------------------------------------|-------|

| b. Odd / Even check with Mux (LSB : $x_0$ )                  | (2pt) |

| c. 8-bit Register with 'clock' signal                        | (5pt) |

| d. Counter with 'start' and 'clock' signal                   | (5pt) |

| e. Combination Logic Circuit – 3X+1 (Adder×2 or 9-bit Adder) | (5pt) |

| f. Combination Logic Circuit – X/2 (Shifter)                 | (5pt) |